信號(hào)發(fā)生器DAC芯片實(shí)現(xiàn)D/A轉(zhuǎn)換方案加工

2020-10-13 17:49:16分類:技術(shù)專題4397

信號(hào)發(fā)生器在通信領(lǐng)域的應(yīng)用,不僅要求信號(hào)發(fā)生器具有較高的穩(wěn)定性和精度,還要能快速切換頻點(diǎn)。本信號(hào)發(fā)生器PCBA方案采用可編程門(mén)陣列(FPGA)設(shè)備與高速D/A芯片相結(jié)合,采用直接數(shù)字合成技術(shù)(DDS法)產(chǎn)生連續(xù)波信號(hào)。DDS技術(shù)是從相位出發(fā)合成波形的技術(shù),打破了傳統(tǒng)頻率合成技術(shù)的束縛,與傳統(tǒng)頻率合成方法相比具有頻率分辨率高、輸出相位噪音低、相位連續(xù)變化和轉(zhuǎn)換速度快等多種優(yōu)點(diǎn),是全數(shù)字技術(shù)的關(guān)鍵隨著微電子技術(shù)和數(shù)字集成電路的發(fā)展,近年來(lái)DDS技術(shù)發(fā)展迅速,廣泛應(yīng)用于數(shù)字通信系統(tǒng)。

原理

利用FPGA完成DDS核的功能,通過(guò)并串轉(zhuǎn)換技術(shù)產(chǎn)生兩路數(shù)字波形數(shù)據(jù),并以低壓差分模式(LVDS)輸出,送入到DAC芯片。最終由DAC芯片經(jīng)過(guò)數(shù)模轉(zhuǎn)換后輸出一定頻率的模擬信號(hào)。

DDS信號(hào)產(chǎn)生單元

DDS的工作原理如圖

主要包括相位累加器、波形存儲(chǔ)器(ROM)、D/A轉(zhuǎn)換器和低通濾波器四個(gè)部分。其中相位累加器與波形存儲(chǔ)由FPGA完成。

在FPGA參考時(shí)鐘的上升沿,相位累加器對(duì)頻率控制字進(jìn)行累加,得到相位對(duì)ROM尋址,完成相位一幅度轉(zhuǎn)換,讀取出相應(yīng)的波形數(shù)據(jù),經(jīng)D/A轉(zhuǎn)換輸出階梯波。

D/A轉(zhuǎn)換

該方案D/A轉(zhuǎn)換采樣樣率高達(dá)2.5GSPS,射頻輸出。

DAC芯片的采樣頻率設(shè)計(jì)為2GSPS,主機(jī)驅(qū)動(dòng)解交錯(cuò)數(shù)據(jù)以偏移二進(jìn)制的格式送到這兩個(gè)接口,每路數(shù)據(jù)的頻率均為芯片時(shí)鐘頻率的1/2,即為1GHz。嵌入式DDR數(shù)據(jù)時(shí)鐘輸入端口(DCI),主機(jī)在DCI時(shí)鐘的上、下邊沿均輸出數(shù)據(jù),DCI時(shí)鐘頻率為500MHz。DCI的時(shí)鐘沿必須與數(shù)據(jù)位躍遷重合。輸人數(shù)據(jù)的標(biāo)稱采樣點(diǎn)是DCI時(shí)鐘沿的中點(diǎn),該點(diǎn)對(duì)應(yīng)于數(shù)據(jù)眼的中心。同時(shí)為實(shí)現(xiàn)主機(jī)對(duì)DAC的同步操作,參考時(shí)鐘4分頻后經(jīng)DCO接口送到主機(jī),該頻率與DCI時(shí)鐘頻率相同。

數(shù)據(jù)匯編器對(duì)接收來(lái)的兩路1GHz的數(shù)據(jù)流進(jìn)行重組,并在DAC核中進(jìn)行數(shù)據(jù)重構(gòu),最終轉(zhuǎn)換為模擬信號(hào)。

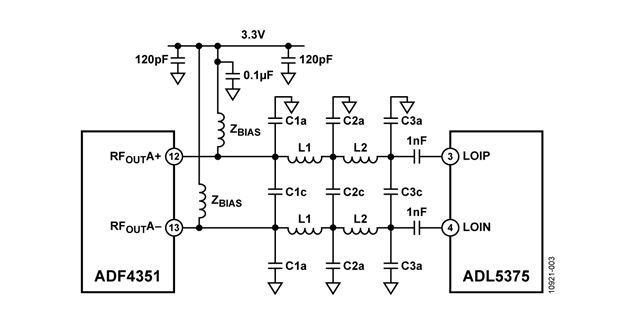

外圍電路

REFIN輸入一個(gè)參考頻率,經(jīng)過(guò)分頻后作為鑒相頻率與鑒相器N分頻后的頻率比較,鑒相器輸出與相位誤差成比例的電壓,經(jīng)過(guò)外部的環(huán)路濾波器控制帶內(nèi)外噪聲與雜散,得到調(diào)諧電壓,通過(guò)VCO使輸出頻率與設(shè)定值相同。輸出同樣是差分信號(hào),經(jīng)過(guò)三端濾波電容連接到時(shí)鐘輸入端口,為其提供穩(wěn)定的工作頻率。

奧芯科技是專業(yè)從事電子產(chǎn)品設(shè)計(jì)、電子方案開(kāi)發(fā)、電子產(chǎn)品PCBA加工的深圳電子方案公司,主要設(shè)計(jì)電子產(chǎn)品包括工控、汽車、電源、通信、安防、醫(yī)療電子產(chǎn)品開(kāi)發(fā)。

公司核心業(yè)務(wù)是提供以工控電子、汽車電子、醫(yī)療電子、安防電子、消費(fèi)電子、通訊電子、電源電子等多領(lǐng)域的電子產(chǎn)品設(shè)計(jì)、方案開(kāi)發(fā)及加工生產(chǎn)的一站式產(chǎn)品研發(fā)生產(chǎn)服務(wù),為滿足不同客戶需求可提供批量產(chǎn)品加工。